Complete project for free Altera Quartus Prime Lite synthesis tool.

Top-level entity is schematic. In project were used free LPM parametrized Altera components and VHDL modules too.

Author: KAMAMI.pl.

Complete project for free Altera Quartus Prime Lite synthesis tool.

Top-level entity is schematic. In project were used free LPM parametrized Altera components and VHDL modules too.

Author: KAMAMI.pl.

Complete project for free Altera Quartus Prime Lite synthesis tool.

Top-level entity is schematic. In project were used free LPM parametrized Altera components and VHDL modules too.

Author: KAMAMI.pl.

- based on classical 7447 (TTL family) 7-segments decoder,

- improved version (VHDL) with modern look of 6 and 9 characters + signalling out-of range input value (>9),

- BIN>HEX decoder described in VHDL.

All examples were tested with 74192 or 74193 up-down counters (TTL family) in complete projects available to download.

Projects are compatible with free Altera Quartus Prime Lite synthesis tool.

Top-level entity is schematic. In project were used free LPM parametrized Altera component (counter) and VHDL modules too.

Author: KAMAMI.pl.

All modules used in project were described in VHDL and are available to download. User manual is available in the above video.

Project is compatible with free Altera Quartus Prime Lite synthesis tool.

Top-level entity is VDHL file.

Author: Paweł Żuk.

Modules used in project were described in VHDL and are available to download. User manual is available in the above video.

Project is compatible with free Altera Quartus Prime Lite synthesis tool.

Top-level entity is VDHL file.

Author: Mariusz Księżak.

Modules used in project were described in VHDL and are available to download. User manual is available in the above video.

Project is compatible with free Altera Quartus Prime Lite synthesis tool.

Top-level entity is VDHL file.

Author: Paweł Żuk.

Simple version of famous Snake game with VGA video output. Two on-board pushbuttons (L, R) are dedicated to change direction of movement of the snake, one is dedicated to restart game. Collected points are displayed on 4-digs/7-segments on-board displays.

Modules used in project were described in VHDL and are available to download. User manual is available in the above video.

Project is compatible with free Altera Quartus Prime Lite synthesis tool.

Top-level entity is VDHL file.

Author: Paweł Żuk.

Project downloadRemote controlled LED-RGB (on-board WS2812B) driver. User can change colour and LED light intensity by 6 hexadecimal characters sent from terminal emulator software running on PC. maXimator board must be equipped with UART/USB converter (like ZL5USB by KAMAMI or similar, based on FTDI or Microchip one-chip protocol converters). Default transmission parameteres: 115 kb/s, 8n1, no flow control.

Modules used in project were described in VHDL and are available to download. User manual is available in the above video.

Project is compatible with free Altera Quartus Prime Lite synthesis tool.

Top-level entity is VDHL file.

Author: Paweł Żuk.

Project downloadSimple DSO (Digital Storage Oscilloscope) based on ADC built-in MAX10 FPGA. In presented example samples frequency is 500 Hz. In each acquistion FPGA collects and displays 1024 samples. Signal shape in displayed on VGA monitor (1024×768/60Hz mode).

Modules used in project were described in VHDL and QSys and are available to download. User manual is available in the above video.

Project is compatible with free Altera Quartus Prime Lite synthesis tool.

Top-level entity is VDHL file.

Author: Piotr Rzeszut, AGH.

Project downloadDigital thermometer with analog STLM20 temperature sensor is based on ADC built-in MAX10 FPGA. In presented example temperature is displayed on 7-seg LED display. Both: displays and temperature sensor are mounted on maXimator shield.

Modules used in project were described in VHDL, top of project is schematic. User manual is available in the above video.

Project is compatible with free Intel Quartus Lite synthesis tool.

Author: Przemysław Sala, AGH.

Project downloadSingle player PONG game implementation is based on maXimator main board and shield, which is included in promotional edition of maXimator eval board. Video signal is generated in HDMI module and described in VHDL, in module with game engine.

In project are used: VHDL module, old-style (from MAX+Plus II) TTL counter 74169 and PLL module generated by QSys. Top of presented project is schematic. User manual is available in the above video.

Project is compatible with free Intel Quartus Lite synthesis tool.

Author: Piotr Chodorowski.

HDMI video generator (vertical stripes in 8 colours, 640×480 pixels @60Hz) described in Verilog HDL. User manual is available in the above video.

Project is compatible with free Intel Quartus Lite 16.1 synthesis tool.

Author: Michał Kozioł.

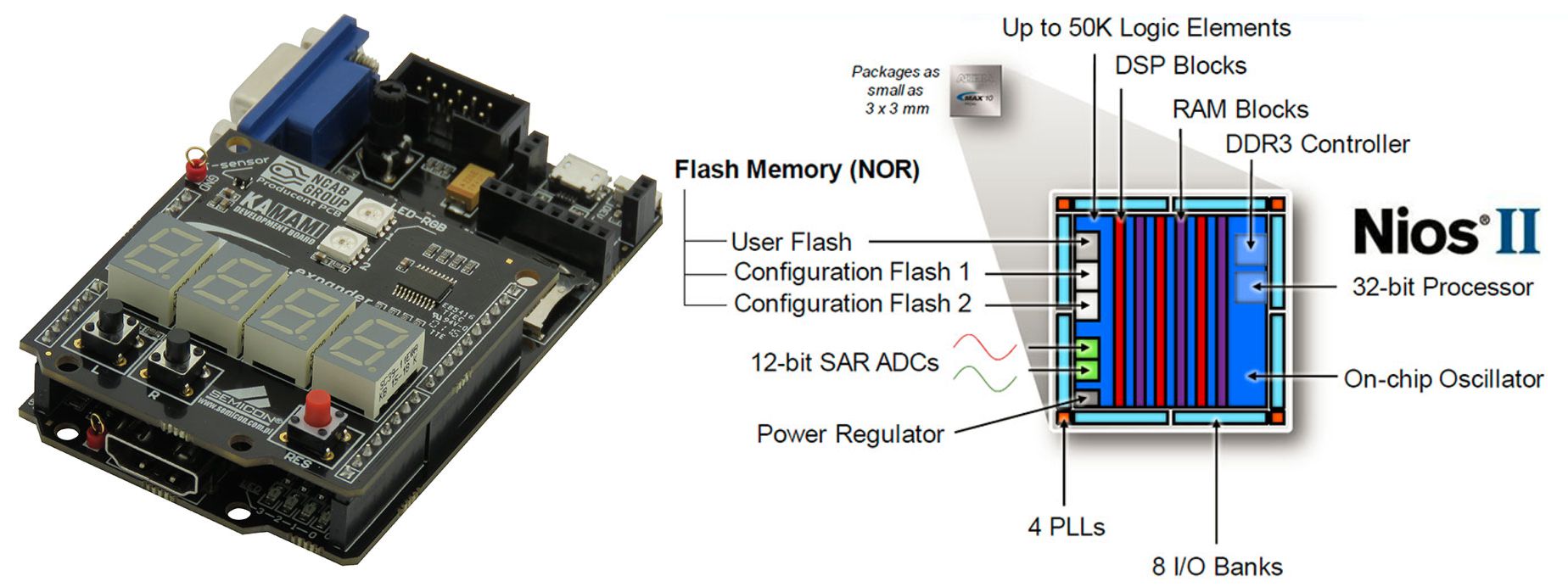

Complete implementation of NIOS II 32 bit RISC processor in maXimator board with simple test application written in C language.

Complete implementation of NIOS II 32 bit RISC processor in maXimator board with simple test application written in C language.

Project is fully compatible with free Intel Quartus Prime 17 synthesis tool.

Author: Mariusz Księżak.

Project downloadFPGA implementation of voltage meter (0-2.5VDC range), based on built-in ADC, with 7-segment LED and VGA displays.

Project is fully compatible with free Intel Quartus Prime 17.1 synthesis tool.

Author: Jakub Tyburski.

Project downloadFPGA implementation of clock synchronized with DCF77 signal. Clock automatically changes winter/summer time. Modules are written in VHDL.

Project is fully compatible with free Intel Quartus Prime 17.1 synthesis tool.

Author: Jakub Tyburski.

Project download